# Lecture 6 Instruction Set Architecture (RISC-V ISA)

Peter Cheung Imperial College London

URL: www.ee.imperial.ac.uk/pcheung/teaching/EE2\_CAS/ E-mail: p.cheung@imperial.ac.uk

# **RISC-V**

- Developed by Krste Asanovic, David Patterson and colleagues at UC Berkeley in 2010

- First widely accepted **open-source** computer architecture

- Underlying design principles:

- **1. Simplicity favours regularity**

- **2.** Make the common case fast

- **3. Smaller is faster**

- 4. Good design demands good compromises

### **Design Principles**

### **Principle 1: Simplicity favors regularity**

- Consistent instruction format

- Same number of operands (two sources and one destination)

- Easier to encode and handle in hardware

### **Principle 2: Make the common case fast**

- RISC-V includes only simple, commonly used instructions

- Hardware to decode and execute instructions can be simple, small, and fast

- More complex instructions (that are less common) performed using multiple simple instructions

- RISC-V is a reduced instruction set computer (RISC), with a small number of simple instructions

- Other architectures, such as Intel's x86, are *complex instruction set computers* (CISC)

### **Principle 3: Smaller is Faster**

H&H p301-303

### **Instructions: Addition & Subtraction**

| C Code     | <b>RISC-V</b> assembly code |

|------------|-----------------------------|

| a = b + c; | add a, b, c                 |

| a = b - c; | sub a, b, c                 |

- Add/sub: mnemonic indicates operation to perform

- b, c: source operands (on which the operation is performed)

- a: destination operand (to which the result is written)

### More complex code is handled by multiple RISC-V instructions.

| C Code         | <b>RISC-V</b> assembly code |

|----------------|-----------------------------|

| a = b + c - d; | add t, b, c $\#$ t = b + c  |

|                | sub a, t, d $\#$ a = t - d  |

Based on: "*Digital Design and Computer Architecture (RISC-V Edition)*" by Sarah Harris and David Harris (H&H),

### **RISC-V** Operands

- **Operand location:** physical location in computer

- Registers

- Memory

- Constants (also called *immediates*)

- RISC-V has 32 32-bit registers

- Registers are faster than memory

- RISC-V called "32-bit architecture" because it operates on 32-bit data

# **32-bit RISC-V Instruction Types**

| Instruction Type   | 31   | 30        | 29 | 28  | 27 | 26  | 25   | 24         | 23  | 22  | 21    | 20   | 19 | 18  | 17  | 16  | 15  | 14   | 13   | 12 | 11 | 10  | 9   | 8    | 7 | 6 | 5 | 4   | 3   | 2  | 1 | 0 |

|--------------------|------|-----------|----|-----|----|-----|------|------------|-----|-----|-------|------|----|-----|-----|-----|-----|------|------|----|----|-----|-----|------|---|---|---|-----|-----|----|---|---|

| Register/register  |      |           | fu | nct | 7  |     |      |            |     | rs2 |       |      |    |     | rs1 |     |     | f    | unct | :3 |    |     | rd  |      |   |   |   | o   | oco | de |   |   |

| Immediate (I-type) | -    |           |    |     | in | nm[ | 11:0 | <b>)</b> ] | •   |     |       |      |    |     | rs1 |     |     | fı   | unc  | :3 |    |     | rd  |      |   |   |   | o   | oco | de |   |   |

| Upper (U-type)     |      | •         |    |     |    |     |      |            | im  | m[3 | 31:12 | 2]   |    |     |     |     |     |      |      |    |    |     | rd  |      |   |   |   | op  | oco | de |   |   |

| Store (S-type)     |      | imm[11:5] |    |     |    |     |      |            |     | rs2 |       |      |    |     | rs1 |     |     | fı   | unc  | :3 |    | im  | n[4 | :0]  |   |   |   | o   | pco | de |   |   |

| Branch (B-type)    | [12] |           |    |     |    |     |      |            | rs2 |     |       |      |    | rs1 |     |     | fı  | unct | 3    | ir | nm | 4:1 | .]  | [11] |   |   | o | oco | de  |    |   |   |

| Jump (J-type)      | [20] |           |    |     | in | nm[ | 10:  | 1]         |     |     |       | [11] |    |     | im  | m[1 | 9:1 | 2]   |      |    |    |     | rd  |      |   |   |   | o   | рсо | de |   |   |

- opcode (7 bit): partially specifies which of the 6 types of instruction formats

- funct7 + funct3 (10 bit): combined with opcode, these two fields describe what operation to perform

- rs1 (5 bit): specifies register containing first operand

- rs2 (5 bit): specifies second register operand

- rd (5 bit):: Destination register specifies register which will receive result of computation

### **RISC-V Registers**

| Name  | Register Number | Usage                              |

|-------|-----------------|------------------------------------|

| zero  | <b>x0</b>       | Constant value 0                   |

| ra    | x1              | Return address                     |

| sp    | x2              | Stack pointer                      |

| gp    | x3              | Global pointer                     |

| tp    | x4              | Thread pointer                     |

| t0-2  | x5-7            | Temporaries                        |

| s0/fp | x8              | Saved register / Frame pointer     |

| s1    | x9              | Saved register                     |

| a0-1  | x10-11          | Function arguments / return values |

| a2-7  | x12-17          | Function arguments                 |

| s2-11 | x18-27          | Saved registers                    |

| t3-6  | x28-31          | Temporaries                        |

# **RISC-V** operand from Registers

| Name  | Register Number | Usage                          |

|-------|-----------------|--------------------------------|

| s0/fp | x8              | Saved register / Frame pointer |

| s1    | x9              | Saved register                 |

| s2-11 | x18-27          | Saved registers                |

C Code RISC-V assembly code

# s0 = a, s1 = b, s2 = ca = b + c; add s0, s1, s2

| a = b + 6; | # s0 = a, s1 = b |

|------------|------------------|

|            | addi s0. s1. 6   |

| Instruction<br>Formats | 31 | 30                      | 29 | 28    | 27 | 26 | 25 | 24 | 23 | 22  | 21 | 20 | 19 | 18 | 17  | 16 | 15 | 14 | 13   | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4  | 3    | 2  | 1 | 0 |

|------------------------|----|-------------------------|----|-------|----|----|----|----|----|-----|----|----|----|----|-----|----|----|----|------|----|----|----|----|---|---|---|---|----|------|----|---|---|

| Register/register      |    |                         | fu | Inct7 | ·  |    |    |    |    | rs2 |    |    |    |    | rs1 |    |    | f  | unct | 3  |    |    | rd |   |   |   |   | ор | ococ | le |   |   |

| Immediate              |    | funct7 rs2<br>imm[11:0] |    |       |    |    |    |    |    |     |    |    |    |    | rs1 |    |    | f  | unct | 3  |    |    | rd |   |   |   |   | ор | coc  | le |   |   |

### **RISC-V** operands from memory

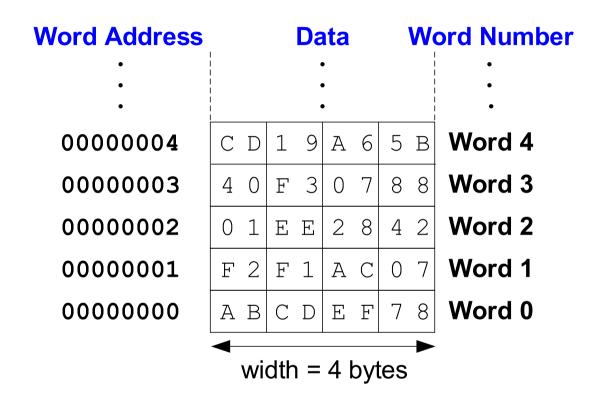

• Each 32-bit data word has a unique address

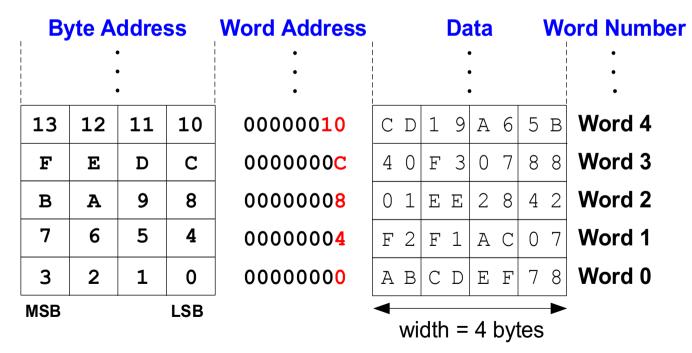

RISC-V uses **byte-addressable** memory (i.e. byte has a unique address), so each 32-bit word uses 4 byte addresses

### **RISC-V Byte-addressable Memory**

- Each data byte has a unique address

- Load/store words or single bytes: load byte (lb) and store byte (sb)

- 32-bit word = 4 bytes, so word address **increments by 4**

Based on: "*Digital Design and Computer Architecture (RISC-V Edition)*" by Sarah Harris and David Harris (H&H),

### **Reading Byte-Addressable Memory**

- **Example:** Load a word of data at memory address 8 into s3.

- s3 holds the value 0x1EE2842 after load

#### **RISC-V** assembly code

lw s3, 8(zero) # read word at address 8 into s3

| Ву             | rte A | <ul> <li>:</li> <li>12</li> <li>11</li> <li>10</li> <li>E</li> <li>D</li> <li>C</li> <li>A</li> <li>9</li> <li>8</li> <li>6</li> <li>5</li> <li>4</li> <li>2</li> <li>1</li> <li>0</li> </ul> | Word Address |                  |           |    | Da  | Ita |    |   | W       | ord Number |        |

|----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|-----------|----|-----|-----|----|---|---------|------------|--------|

| <br> <br>      | •     | •                                                                                                                                                                                             |              | •                | <br> <br> |    |     | •   | •  |   |         |            | •      |

| <br> <br> <br> | •     | •                                                                                                                                                                                             |              | •                |           |    |     | •   | •  |   |         |            | •      |

| 13             | 12    | 11                                                                                                                                                                                            | 10           | 00000010         | С         | D  | 1   | 9   | А  | 6 | 5       | В          | Word 4 |

| F              | E     | D                                                                                                                                                                                             | С            | 000000c          | 4         | 0  | F   | 3   | 0  | 7 | 8       | 8          | Word 3 |

| В              | A     | 9                                                                                                                                                                                             | 8            | 8000000          | 0         | 1  | E   | E   | 2  | 8 | 4       | 2          | Word 2 |

| 7              | 6     | 5                                                                                                                                                                                             | 4            | 00000004         | F         | 2  | F   | 1   | A  | С | 0       | 7          | Word 1 |

| 3              | 2     | 1                                                                                                                                                                                             | 0            | 00000000         | A         | В  | С   | D   | Ε  | F | 7       | 8          | Word 0 |

| MSB            |       |                                                                                                                                                                                               | LSB          | _<br>/ Edition)" | 4         | wi | dth | ) = | 41 |   | -<br>PQ |            |        |

Based on: "Digital Design and Computer Architecture (RISC-V Edition)" by Sarah Harris and David Harris (H&H),

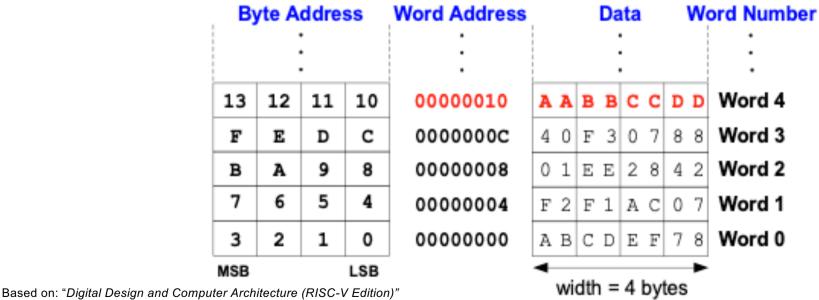

# Writing Byte-Addressable Memory

- **Example:** store the value held in t7 into memory address 0x10 (16)

- if t7 holds the value 0xAABBCCDD, then after the sw completes, word 4 (at address 0x10) in memory will contain that value

#### **RISC-V** assembly code

SW t7, 0x10(zero) # write t7 into address 16

by Sarah Harris and David Harris (H&H),

## **RISC-V: Operands from Constants**

• 12-bit signed constants (immediates) using addi:

C Code

RISC-V assembly code

// int is a 32-bit signed word

# s0 = a, s1 = b

int a = -372;

addi s0, zero, -372

int b = a + 6;

addi s1, s0, 6

372 = 12'h174 = 12'b0001\_0111\_0100

-372 = 12'b1110\_1000 = 12'hE8B

• Form 32-bit constant using sign extension

| Instruction<br>Formats | 31 | 30 | 29 | 28 | 27 | 26  | 25     | 24 | 23 | 22  | 21  | 20 | 19 | 18 | 17  | 16 | 15 | 14 | 13   | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|------------------------|----|----|----|----|----|-----|--------|----|----|-----|-----|----|----|----|-----|----|----|----|------|----|----|----|----|---|---|---|---|----|-----|---|---|---|

| Immediate              |    |    |    |    |    | imm | [11:0] | ]  | 12 | 'hE | E8B |    |    |    | rs1 |    |    | f  | unct | 3  |    |    | rd |   |   |   |   | ор | cod | e |   |   |

Any immediate that needs **more than 12 bits** cannot use this method.

# **RISC-V: Operand with 32-bit Constants**

- Use load upper immediate (lui) and addi

- lui: puts an immediate in the upper 20 bits of destination register and 0's in lower 12 bits

#### C Code

int  $a = 0 \times FEDC8765$ ;

#### **RISC-V** assembly code

# s0 = a

lui s0, 0xFEDC8

addi s0, s0, 0x765

#### Remember that addi sign-extends its 12-bit immediate constant

| Instruction<br>Formats | 31 | 30 | 29         | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6   | 5  | 4 | 3 | 2 | 1 |

|------------------------|----|----|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|----|-----|----|---|---|---|---|

| Upper<br>Immediate     |    |    | imm[31:12] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | rd |    |    |   |   | ор | cod | le |   |   |   |   |

# **RISC-V: 32-bit Constants (bit 11 is 1)**

If bit 11 of the constant is 1, increment upper 20 bits by 1 in lui

#### C Code

int a = 0xFEDC8EAB;

**Note:** -341 = 0xEAB

#### **RISC-V** assembly code

# s0 = alui s0, 0xFEDC9 # s0 = 0xFEDC9000addi s0, s0, -341 # s0 = 0xFEDC9000 + 0xFFFFFEAB# = 0xFEDC8EAB

Based on: "*Digital Design and Computer Architecture (RISC-V Edition)*" by Sarah Harris and David Harris (H&H),

## **RISC-V:** Psuedoinstruction

- Load immediate 32-bit word is tedious.

- Pseudoinstruction Assembler program translate "Load Immediate" instruction "li" to two real RISC-V instructions: "lui" and "addi"

#### C Code

int a = 0xFEDC8EAB;

**Note:** -341 = 0xEAB

#### **RISC-V** pseudoinstructions

# s0 = a

li s0, 0xFEDC<mark>8E</mark>AB

#### **RISC-V** real instructions

# s0 = a

lui s0, 0xFEDC9

addi s0, s0, 0xEAB

• RISC-V has many pseudoinstructions (see later lectures)

### How do we address the operands?

- Register Only

- Immediate

- Base Addressing

- PC-Relative

### **Register Only**

- Operands found in registers

- Example: add s0, t2, t3

- Example: sub t6, s1, 0

### Immediate

- 12-bit signed immediate used as an operand

- **Example:** addi s4, t5, -73

- Example: ori t3, t7, 0xFF

### **RISC-V:** Base + Offset Addressing

### **Base Addressing**

- Loads and Stores

- Address of operand is: base address + immediate

- Example: lw s4, 72(zero)

- address = 0 + 72

- Example: sw t2, -25(t1)

- address = t1 25

# PC-Relative Addressing: branches and jal

Example:

| Address |     | Instruction    |

|---------|-----|----------------|

| 0x354   | L1: | addi s1, s1, 1 |

| 0x358   |     | sub t0, t1, s7 |

| •••     |     | •••            |

| 0xEB0   |     | bne s8, s9, L1 |

The label is (0xEB0-0x354) = 0xB5C (2908) instructions before bne

### **RISC-V: Instruction coding for Branch offset**

|                 | /  | Ass  | en | nb | ly   |      |    |     |    |    |    | F  | Re         | at | ive | e o | off | se | et = | = - | 29 | 90  | 8    |   |      |   |   |    |     |          |   |   |  |

|-----------------|----|------|----|----|------|------|----|-----|----|----|----|----|------------|----|-----|-----|-----|----|------|-----|----|-----|------|---|------|---|---|----|-----|----------|---|---|--|

|                 |    |      |    |    |      |      |    |     | ir | nm |    |    | 290<br>mbe |    |     |     |     |    |      |     |    |     |      |   |      |   |   |    |     | 0 )<br>1 |   |   |  |

| Instru<br>Forma |    |      |    |    |      | 26   | 25 | 24  | 23 | 22 | 21 | 20 | 19         | 18 | 17  | 16  | 15  | 14 | 13   | 12  | 11 | 10  | 9    | 8 | 7    | 6 | 5 | 4  | 3   | 2        | 1 | 0 |  |

| Branc           | :h | [12] |    |    | imm[ | 10:5 | ]  | rs2 |    |    |    |    |            |    | rs1 |     |     | f  | unct | 3   | i  | mm[ | 4:1] | ] | [11] |   |   | ор | cod | le       |   |   |  |

### **Field Values**

| imm <sub>12,10:5</sub> | rs2    | rs1    | funct3 | $imm_{4:1,11}$ | ор     |

|------------------------|--------|--------|--------|----------------|--------|

| 1100 101               | 24     | 25     | 1      | 0010 0         | 99     |

| 7 bits                 | 5 bits | 5 bits | 3 bits | 5 bits         | 7 bits |

### **Machine Code**

| imm <sub>12,10:5</sub> | , rs2  | rs1    | funct3 | imm <sub>4:1,1</sub> | 1 <mark>op</mark> |              |

|------------------------|--------|--------|--------|----------------------|-------------------|--------------|

| 1100 101               | 11000  | 11001  | 001    | 0010 <mark>0</mark>  | 110 0011          | (0xCB8C9263) |

| 7 bits                 | 5 bits | 5 bits | 3 bits | 5 bits               | 7 bits            |              |

# **R-type Instructions: 3 register instructions**

| Instruction<br>Formats | 31 | 30 | 29 | 28    | 27 | 26 | 25 | 24 | 23 | 22  | 21 | 20 | 19 | 18 | 17  | 16 | 15 | 14 | 13   | 12 | <mark>1</mark> 1 | 10 | 9  | 8 | 7 | 6 | 5 | 4  | 3   | 2  | 1 | 0 |

|------------------------|----|----|----|-------|----|----|----|----|----|-----|----|----|----|----|-----|----|----|----|------|----|------------------|----|----|---|---|---|---|----|-----|----|---|---|

| Register/register      |    |    | fu | unct7 | 7  |    |    |    |    | rs2 |    |    |    |    | rs1 |    |    | f  | unct | 3  |                  |    | rd |   |   |   |   | ор | cod | le |   |   |

| funct3 | funct7                                                          | Туре                                                                                                                                                                                                                                                                                                                                                          | Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000    | 0000000                                                         | R                                                                                                                                                                                                                                                                                                                                                             | add rd, rs1, rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rd = rs1 + rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 000    | 0100000                                                         | R                                                                                                                                                                                                                                                                                                                                                             | sub rd, rs1, rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | sub                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rd = rs1 - rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 001    | 0000000                                                         | R                                                                                                                                                                                                                                                                                                                                                             | sll rd, rs1, rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | shift left logical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | rd = rs1 << rs2 <sub>4:0</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 010    | 0000000                                                         | R                                                                                                                                                                                                                                                                                                                                                             | slt rd, rs1, rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | set less than                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | rd = (rs1 < rs2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 011    | 0000000                                                         | R                                                                                                                                                                                                                                                                                                                                                             | sltu rd, rs1, rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | set less than unsigned                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | rd = (rs1 < rs2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 100    | 0000000                                                         | R                                                                                                                                                                                                                                                                                                                                                             | xor rd, rs1, rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rd = rs1 ^ rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 101    | 0000000                                                         | R                                                                                                                                                                                                                                                                                                                                                             | srl rd, rs1, rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | shift right logical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $rd = rs1 >> rs2_{4:0}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 101    | 0100000                                                         | R                                                                                                                                                                                                                                                                                                                                                             | sra rd, rs1, rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | shift right arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $rd = rs1 >>> rs2_{4:0}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 110    | 0000000                                                         | R                                                                                                                                                                                                                                                                                                                                                             | or rd, rs1, rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | rd = rs1   rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 111    | 0000000                                                         | R                                                                                                                                                                                                                                                                                                                                                             | and rd, rs1, rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rd = rs1 & rs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | )000<br>)000<br>)011<br>)100<br>)11<br>100<br>101<br>101<br>110 | 000         0000000           000         0100000           001         0000000           010         0000000           011         0000000           011         0000000           011         0000000           011         0000000           011         0000000           011         0000000           011         0000000           011         0100000 | 000         00000000         R           000         0100000         R           001         0000000         R           010         0000000         R           010         0000000         R           011         0000000         R           010         0000000         R           011         0000000         R           011         0000000         R           011         01000000         R           011         01000000         R           011         01000000         R           011         01000000         R | 000         00000000         R         add         rd,         rs1,         rs2           000         0100000         R         sub         rd,         rs1,         rs2           001         0000000         R         sll         rd,         rs1,         rs2           010         0000000         R         sll         rd,         rs1,         rs2           010         0000000         R         slt         rd,         rs1,         rs2           010         0000000         R         slt         rd,         rs1,         rs2           011         0000000         R         sltu         rd,         rs1,         rs2           010         0000000         R         sltu         rd,         rs1,         rs2           010         0000000         R         srl         rd,         rs1,         rs2           011         0000000         R         srl         rd,         rs1,         rs2           011         0100000         R         sra         rd,         rs1,         rs2           010         0000000         R         or         rd,         rs1,         rs2 | 000         0000000         R         add         rd,         rs1,         rs2         add           000         0100000         R         sub         rd,         rs1,         rs2         sub           001         0000000         R         sll         rd,         rs1,         rs2         sub           001         0000000         R         sll         rd,         rs1,         rs2         shift left logical           010         0000000         R         slt         rd,         rs1,         rs2         set less than           010         0000000         R         sltu         rd,         rs1,         rs2         set less than           011         0000000         R         sltu         rd,         rs1,         rs2         set less than unsigned           100         0000000         R         xor         rd,         rs1,         rs2         shift right logical           101         0100000         R         sra         rd,         rs1,         rs2         shift right arithmetic           101         0100000         R         or         rd,         rs1,         rs2         or |

# I & S-type Instructions: All involve imm constants

| Instruction<br>Formats | 31     | 30 | 0 29  | 28       | 27  | 26  | 25     | 24   | 23  | 22   | 21  | 20  | 19     | 18    | 17     | 16     | 15   | 14   | 13    | 12  | 11   | 10   | 9     | 8  | 7                | 6   | 5   | 4    | 3 2  | 2 1 | 0 |

|------------------------|--------|----|-------|----------|-----|-----|--------|------|-----|------|-----|-----|--------|-------|--------|--------|------|------|-------|-----|------|------|-------|----|------------------|-----|-----|------|------|-----|---|

| Immediate              |        |    |       |          |     | imm | [11:0] | ]    |     |      |     |     |        |       | rs1    |        |      |      | funct | 3   |      |      | rd    |    |                  |     |     | op   | code | •   |   |

| Store                  |        |    | imr   | n[11     | :5] |     |        |      |     | rs2  | 2   |     |        |       | rs1    |        |      |      | func  | t3  |      | im   | m[4:  | 0] |                  |     |     | ор   | code | 9   |   |

| op                     | funct3 | f  | unct7 |          | Ty  | pe  | Instru | ıcti | on  |      |     |     | Desc   | ript  | ion    |        |      |      |       | 0   | рега | tion |       |    |                  |     |     |      |      |     |   |

| 0000011 (3)            | 000    | -  |       |          | Ι   |     | lb     | r    | d,  | imm( | (rs | 1)  | load   | byt   | с      |        |      |      |       | rc  | =    | Sig  | gnEx  | t( | [Add             | lre | ss] | 7:0) |      |     |   |

| 0000011 (3)            | 001    | -  |       |          | Ι   |     | lh     | r    | d,  | imm( | (rs | 1)  | load   | hal   | f      |        |      |      |       | rc  | =    | Sig  | gnEx  | t( | [Add             | Ire | ss] | 15:0 | )    |     | _ |

| 0000011 (3)            | 010    | -  |       |          | I   |     | ۱w     | r    | d,  | imm( | (rs | 1)  | load   | wo    | rd     |        |      |      |       | rc  | =    |      |       |    | [Add             | ire | ss] | 31:0 |      |     |   |

| 0000011 (3)            | 100    | -  |       |          | Ι   |     | lbu    | r    | d,  | imm( | (rs | 1)  | load   | byt   | e uns  | signe  | ed   |      |       | rc  | =    | Zer  | roEx  | t( | [Add             | Ire | ss] | 7:0) |      |     |   |

| 0000011 (3)            | 101    | -  |       |          | I   |     | lhu    | r    | d,  | imm( | (rs | 1)  | load   | hal   | f uns  | igne   | d    |      |       | rc  | =    | Zei  | roEx  | t( | [Add             | Ire | ss] | 15:0 | )    |     |   |

| 0010011 (19)           | 000    | -  |       |          | I   |     | addi   | r    | d,  | rs1, | , i | mm  | add    | imn   | nedia  | te     |      |      |       | rc  | =    | rs!  | 1 +   |    | Sigr             | Ex  | t(i | mm ) |      |     |   |

| 0010011 (19)           | 001    | 0  | 00000 | $00^{*}$ | Ι   |     | slli   | r    | d,  | rs1, | , u | imm | shift  | left  | logi   | cal in | mm   | edia | ite   | rc  | =    | rsi  | 1 <<  |    | uimn             | ı   |     |      |      |     |   |

| 0010011 (19)           | 010    | -  |       |          | Ι   |     | slti   | r    | d,  | rs1, | , i |     |        |       | han    |        |      |      |       | rc  | =    | (rs1 | 1 <   |    | Sign             | Ex  | t(i | mm ) | )    |     |   |

| 0010011 (19)           | 011    | -  |       |          | I   |     | slti   | u r  | d,  | rs1, | , i | mm  | set le | ess t | han    | imm    | . un | sig  | ned   | rc  | =    | (rs) | 1 <   |    | Sign             | Ex  | t(i | mm ) | )    |     |   |

| 0010011 (19)           | 100    | -  |       |          | I   |     | xori   | r    | d,  | rs1, | , i | mm  | xor    | imm   | edia   | te     |      |      |       | rc  | =    | rsi  | 1 ^   |    | Sigr             | ιEx | t(i | mm ) |      |     |   |

| 0010011 (19)           | 101    | 0  | 00000 | 00*      | Ι   |     | srli   | r    | d,  | rs1, | , u | imm | shift  | rigl  | nt log | gical  | imr  | med  | iate  | rc  | =    | rsi  | 1 >>  |    | uimn             | 1   |     |      |      |     |   |

| 0010011 (19)           | 101    | 0  | 01000 | $00^{*}$ | Ι   |     | srai   | r    | d,  | rs1, | , u |     |        |       | nt ari | -      |      | _    |       | rc  | =    | rs!  | 1 >>  | >  | uimn             | 1   |     |      |      |     |   |

| 0010011 (19)           | 110    | -  |       |          | I   |     | ori    | r    | d,  | rs1, | , i |     |        | -     | diate  |        |      |      |       | rc  | =    | rsi  | 1     |    | Sigr             | ιEx | t(i | mm ) |      |     |   |

| 0010011 (19)           | 111    | -  |       |          | Ι   |     | andi   | r    | d,  | rs1, | , i | mm  | and    | imn   | nedia  | te     |      |      |       | rc  | =    | rsi  | 1 &   |    | Sigr             | Еx  | t(i | mm ) |      |     |   |

| 0100011 (35)           | 000    | -  | _     |          | S   |     | sb     | r    | s2, | imm( | (rs | 1)  | store  | e by  | te     |        |      |      |       | [ A | ddr  | ess  | ]7:0  | =  | rs27             | :0  |     |      |      |     | _ |

| 0100011 (35)           | 001    | -  | -     |          | S   |     | sh     | r    | s2, | imm( | (rs | 1)  | store  | e ha  | lf     |        |      |      |       | [A  | ddr  | ess  | ]15:0 | -  | rs2 <sub>1</sub> | 5:0 |     |      |      |     |   |

| 0100011 (35)           | 010    | -  | -     |          | S   |     | SW     | r    | s2, | imm( | (rs | 1)  | store  | e wo  | ord    |        |      |      |       | [A  | ddr  | ess  | ]31:0 | =  | rs2              |     |     |      |      |     |   |

PYKC 29 Oct 2024

### **B-type Instructions: PC-relative Branches**

| Instruction<br>Formats | 31   | 30 | 29 | 28   | 27   | 26 | 25 | 24 | 23 | 22  | 21 | 20 | 19 | 18 | 17  | 16 | 15 | 14 | 13   | 12 | 11 | 10   | 9    | 8 | 7    | 6 | 5 | 4  | 3   | 2  | 1 | ο |

|------------------------|------|----|----|------|------|----|----|----|----|-----|----|----|----|----|-----|----|----|----|------|----|----|------|------|---|------|---|---|----|-----|----|---|---|

| Branch                 | [12] |    | 1  | imm[ | 10:5 | ]  |    |    |    | rs2 |    |    |    |    | rs1 |    |    | f  | unct | 3  | i  | mm[4 | 4:1] |   | [11] |   |   | op | coo | le |   |   |

| ор           | funct3 | funct7 | Туре | Instruction          | Description               | Operation                |

|--------------|--------|--------|------|----------------------|---------------------------|--------------------------|

| 1100011 (99) | 000    | -      | В    | beq rs1, rs2, label  | branch if =               | if (rs1 == rs2) PC = BTA |

| 1100011 (99) | 001    | -      | В    | bne rs1, rs2, label  | branch if ≠               | if (rs1 ≠ rs2) PC = BTA  |

| 1100011 (99) | 100    | -      | В    | blt rs1, rs2, label  | branch if <               | if (rs1 < rs2) PC = BTA  |

| 1100011 (99) | 101    | -      | В    | bge rs1, rs2, label  | branch if ≥               | if (rs1 ≥ rs2) PC = BTA  |

| 1100011 (99) | 110    | -      | В    | bltu rs1, rs2, label | branch if < unsigned      | if (rs1 < rs2) PC = BTA  |

| 1100011 (99) | 111    | -      | В    | bgeu rs1, rs2, label | branch if $\geq$ unsigned | if (rs1 ≥ rs2) PC = BTA  |

## U & I -type Instructions: Upper & Jump/Link

| Instruction<br>Formats | 31   | 30 | 29 | 28 | 27 | 26  | 25    | 24 | 23 | 22   | 21    | 20   | 19 | 18 | 17 | 16   | 15   | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|------------------------|------|----|----|----|----|-----|-------|----|----|------|-------|------|----|----|----|------|------|----|----|----|----|----|----|---|---|---|---|----|-----|---|---|---|

| Upper<br>Immediate     |      |    |    |    |    |     |       |    | ir | nm[3 | 31:12 | 2]   |    |    |    |      |      |    |    |    |    |    | rd |   |   |   |   | ор | cod | е |   |   |

| Jump                   | [20] |    |    |    | i  | mm[ | 10:1] | ]  |    |      |       | [11] |    |    | in | nm[1 | 9:12 | 2] |    |    |    |    | rd |   |   |   |   | ор | cod | е |   |   |

| op            | funct3 | funct7 | Туре | Instruction       | Description               | Operation                            |

|---------------|--------|--------|------|-------------------|---------------------------|--------------------------------------|

| 0010111 (23)  | -      | -      | U    | auipc rd, upimm   | add upper immediate to PC | rd = {upimm, 12'b0} + PC             |

| 0110111 (55)  | -      | -      | U    | lui rd, upimm     | load upper immediate      | rd = {upimm, 12'b0}                  |

| 1100111 (103) | 000    | -      | Ι    | jalr rd, rs1, imm | jump and link register    | PC = rs1 + SignExt(imm), rd = PC + 4 |

| 1101111 (111) | -      | -      | J    | jal rd, label     | jump and link             | PC = JTA, $rd = PC + 4$              |

• We will discuss auipc, jalr and jal instructions in another lecture

### **RISC-V** Arithmetic instructions

| ,       | Inemonic      | Instruction                         | Туре | Description              |

|---------|---------------|-------------------------------------|------|--------------------------|

| ADD r   | rd, rs1, rs2  | Add                                 | R    | rd ← rs1 + rs2           |

| SUB n   | d, rs1, rs2   | Subtract                            | R    | rd ← rs1 - rs2           |

| ADDI n  | d, rs1, imm12 | Add immediate                       | I    | rd ← rs1 + imm12         |

| SLT r   | d, rs1, rs2   | Set less than                       | R    | rd ← rs1 < rs2 ? 1 : 0   |

| SLTI r  | d, rs1, imm12 | Set less than immediate             | Т    | rd ← rs1 < imm12 ? 1 : 0 |

| SLTU r  | d, rs1, rs2   | Set less than unsigned              | R    | rd ← rs1 < rs2 ? 1 : 0   |

| SLTIU r | d, rs1, imm12 | Set less than<br>immediate unsigned | I.   | rd ← rs1 < imm12 ? 1 : 0 |

| LUI r   | d, imm20      | Load upper immediate                | U    | rd ← imm20 << 12         |

| AUIP rd | l, imm20      | Add upper immediate<br>to PC        | U    | rd ← PC + imm20 << 12    |

### **RISC-V** Logic instructions

| Mnemonic            | Instruction                      | Туре | Description       |

|---------------------|----------------------------------|------|-------------------|

| AND rd, rs1, rs2    | AND                              | R    | rd ← rs1 & rs2    |

| OR rd, rs1, rs2     | OR                               | R    | rd ← rs1   rs2    |

| XOR rd, rs1, rs2    | XOR                              | R    | rd ← rs1 ^ rs2    |

| ANDI rd, rs1, imm12 | AND immediate                    | I.   | rd ← rs1 & imm12  |

| ORI rd, rs1, imm12  | OR immediate                     | T    | rd ← rs1   imm12  |

| XORI rd, rs1, imm12 | XOR immediate                    | I    | rd ← rs1 ^ imm12  |

| SLL rd, rs1, rs2    | Shift left logical               | R    | rd ← rs1 << rs2   |

| SRL rd, rs1, rs2    | Shift right logical              | R    | rd ← rs1 >> rs2   |

| SRA rd, rs1, rs2    | Shift right arithmetic           | R    | rd ← rs1 >> rs2   |

| SLLI rd, rs1, shamt | Shift left logical<br>immediate  | I.   | rd ← rs1 << shamt |

| SRLI rd, rs1, shamt | Shift right logical imm.         | I    | rd ← rs1 >> shamt |

| SRAI rd, rs1, shamt | Shift right arithmetic immediate | I    | rd ← rs1 >> shamt |

# **RISC-V** Load/Store instructions

| Mnemonic           | Instruction               | Туре | Description                  |

|--------------------|---------------------------|------|------------------------------|

| LW rd, imm12(rs1)  | Load word                 | I    | rd ← mem[rs1 + imm12]        |

| LH rd, imm12(rs1)  | Load halfword             | 1    | rd ← mem[rs1 + imm12]        |

| LB rd, imm12(rs1)  | Load byte                 | I.   | rd ← mem[rs1 + imm12]        |

| LWU rd, imm12(rs1) | Load word unsigned        | I.   | rd ← mem[rs1 + imm12]        |

| LHU rd, imm12(rs1) | Load halfword<br>unsigned | I    | rd ← mem[rs1 + imm12]        |

| LBU rd, imm12(rs1) | Load byte unsigned        | I,   | rd ← mem[rs1 + imm12]        |

| SW rs2, imm12(rs1) | Store word                | s    | rs2(31:0) → mem[rs1 + imm12] |

| SH rs2, imm12(rs1) | Store halfword            | s    | rs2(15:0) → mem[rs1 + imm12] |

| SB rs2, imm12(rs1) | Store byte                | s    | rs2(7:0) → em[rs1 + imm12]   |

### **RISC-V Branch & Jump instructions**

| Mnemonic             | Instruction                           | Туре | Description                          |

|----------------------|---------------------------------------|------|--------------------------------------|

| BEQ rs1, rs2, imm12  | Branch equal                          | SB   | if rs1 == rs2<br>pc ← pc + imm12     |

| BNE rs1, rs2, imm12  | Branch not equal                      | SB   | if rs1 != rs2<br>pc ← pc + imm12     |

| BGE rs1, rs2, imm12  | Branch greater than or equal          | SB   | if rs1 >= rs2<br>pc ← pc + imm12     |

| BGEU rs1, rs2, imm12 | Branch greater than or equal unsigned | SB   | if rs1 >= rs2<br>pc ← pc + imm12     |

| BLT rs1, rs2, imm12  | Branch less than                      | SB   | if rs1 < rs2<br>pc ← pc + imm12      |

| BLTU rs1, rs2, imm12 | Branch less than<br>unsigned          | SB   | if rs1 < rs2<br>pc ← pc + imm12 << 1 |

| JAL rd, imm20        | Jump and link                         | IJ   | rd ← pc + 4<br>pc ← pc + imm20       |

| JALR rd, imm12(rs1)  | Jump and link register                | I    | rd ← pc + 4<br>pc ← rs1 + imm12      |

### **RISC-V** Psuedoinstructions

| Mnemonic              | Instruction                       | Base instruction(s)                            | Mnemonic         | Instruction            | Base inst                      |

|-----------------------|-----------------------------------|------------------------------------------------|------------------|------------------------|--------------------------------|

| LI rd, imm12          | Load immediate (near)             | ADDI rd, zero, imm12                           | BEQZ rs1, offset | Branch if rs1 = 0      | BEQ rs1, zero                  |

| LI rd, imm            | Load immediate (far)              | LUI rd, imm[31:12]<br>ADDI rd, rd, imm[11:0]   | BNEZ rs1, offset | Branch if rs1 ≠ 0      | BNE rs1, zero                  |

| LA rd, sym            | Load address (far)                | AUIPC rd, sym[31:12]<br>ADDI rd, rd, sym[11:0] | BGEZ rs1, offset | Branch if $rs1 \ge 0$  | BGE rs1, zero                  |

| MV rd, rs             | Copy register                     | ADDI rd, rs, 0                                 | DIFT and affect  | Branch if rs1 ≤ 0      | DCE                            |

| NOT rd, rs            | One's complement                  | XORI rd, rs, -1                                | BLEZ rs1, offset |                        | BGE zero, rs1                  |

| NEG rd, rs            | Two's complement                  | SUB rd, zero, rs                               | BGTZ rs1, offset | Branch if rs1 > 0      | BLT zero, rs1                  |

| BGT rs1, rs2, offset  | Branch if rs1 > rs2               | BLT rs2, rs1, offset                           | J offset         | Unconditional jump     | JAL zero, off:                 |

| BLE rs1, rs2, offset  | Branch if rs1 ≤ rs2               | BGE rs2, rs1, offset                           | CALL offset12    | Call subroutine (near) | JALR ra, ra, d                 |

| BGTU rs1, rs2, offset | Branch if rs1 > rs2<br>(unsigned) | BLTU rs2, rs1, offset                          | CALL offset      | Call subroutine (far)  | AUIPC ra, offs<br>JALR ra, ra, |

| BLEU rs1, rs2, offset | Branch if rs1 ≤ rs2<br>(unsigned) | BGEU rs2, rs1, offset                          | RET              | Return from subroutine | JALR zero, 0(r                 |

|                       | (ansigned)                        |                                                | NOP              | No operation           | ADDI zero, zer                 |